INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING ol. 4. Issue 6. June 2016

# Implementation of Modulation Techniques for Inverters

Jaspreet Dhillon<sup>1</sup>, Darshan Singh<sup>2</sup>, Daljit Kaur<sup>3</sup>

PG Student (Power Engineering), Dept of EE, GZS campus CET, Bathinda, Punjab, India<sup>1</sup>

Principal, Govt. Polytechnic College, Bathinda, Punjab, India<sup>2</sup>

Assistant Professor, Dept of EE, GZS campus CET, Bathinda, Punjab, India<sup>3</sup>

Abstract: Multilevel inverter technology has emerged in recent times as a very important in the area of highpower medium-voltage energy control. In this paper, cascaded multilevel inverter is used to reduce the total harmonic distortion. A cascaded multilevel inverter consists of series Hbridge (single-phase, full-bridge) inverter units. Pulse Width Modulation (PWM) inverters play a major role in the field of power electronics. Space Vector Modulation (SVM) is the popular PWM method and possibly the best among all the PWM techniques as it generates higher voltages with low total harmonic distortion .This paper comprehensively analyzes the relationship between spacevector modulation and three-phase sine pulse width modualtion (PWM). The simulation is done by MATLAB Simulink software.

Keywords: Cascaded Multilevel Inverter, Sinepulse width modulation, Space- vector pulsewidth modulation.

# **I. INTRODUCTION**

with typical and very well known two-level converters. These advantages are fundamentally focused on improvements in the output signals quality and a nominal power increase in the converter. These properties make multilevel converters very attractive to the industry and nowadays, researchers all over the world are spending great efforts trying to improve multilevel converters performance as the control simplification and the performance of different optimization algorithms in order to enhance the Total Harmonic Distortion (THD) of the output signals.

Plentiful multilevel converter topologies have been proposed during the last two decades. In this paper we have discussed mainly three different major multilevel converter structures: cascaded H-bridges converter, diode clamped and flying capacitors. Moreover, abundant modulation techniques and control paradigms have been developed for multilevelconverters but main focus of the thesis is around sinusoidal pulse width modulation (SPWM) and space vector modulation(SVM).

## **II. MULTILEVEL INVERTERS**

## A. General

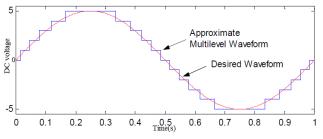

Multilevel inverter is divide the main dc supply voltage into several smaller dc sources which are used to synthesize an ac voltage into staircase, or stepped, approximation of the desired sinusoidal waveform. A waveform generated with five dc-sources each with onevolt magnitude approximates the desired sinusoid, as shown in figure 1. The five dc sources (five steps) produce a peak to peak voltage of 10 volts using 11 discrete levels. levels are 2n+1, where n is the number of cells. The Figure 1 illustrates an example multilevel waveform. switching angles can be chosen in such a way that the total Using multiple levels, the multilevel inverter can yield

Multilevel converters present great advantages compared operating characteristics such a high voltages, high power levels, and high efficiency without the use of transformers.

Fig1 Example multilevel sinusoidal approximation using 11-Levels

The multilevel inverter combines individual dc sources at specified times to yield a sinusoidal resemblance; by using more steps to synthesize the sinusoidal waveform, the waveform approaches the desired sinusoid and the total harmonic distortion approaches zero.

## B. Types Of Multilevel Inverter

There are three main types of multilevel inverter: (1) diode-clamped inverter, (2) capacitor-clamped inverter, and (3) Cascaded inverter. The multilevel inverter may be implemented at the discrete component level dividing the main dc supply voltage into smaller voltages.

## C. Cascade H-Bridge Inverter

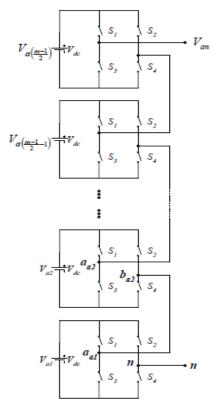

The concept of this inverter is based on connecting Hbridge inverters in series to get a sinusoidal voltage output. The output voltage is the sum of the voltage that is generated by each cell. The number of output voltage harmonic distortion is minimized. One of the advantages

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING

Vol. 4. Issue 6. June 2016 of this type of multilevel inverter is that it needs less 3. Potential of electrical shock is reduced due to the

number of components comparative to the Diode clamped or the flying capacitor, so the price and the weight of the 4. inverter is less than that of the two former types.

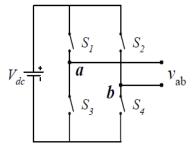

Fig. 2 Single H-bridge configuration

An n level cascaded H-bridge multilevel inverter needs 2(n-1) switching devices where n is the number of the output voltage level. The four switches S1, S2, S3 and S4 controlled to generate three discrete outputs Vab with levels of -Vdc, 0, +Vdc. When S2 and S3 are on the output is -Vdc; When either pair S1 and S2 or S3 and S4 are on the output is 0; when S1 and S4 are turned on the output is +Vdc.

Fig. 3. Cascaded H-bridge multilevel inverter

Advantages of cascade multilevel H-bridge inverter with s separate dc source per phase are as follows

1. The series structure allows a scalable, modularized circuit layout and packaging since each bridge has the same structure.

2. Switching redundancy for inner voltage levels is possible because the phase voltage output is sum of each bridge's output.

separate dc sources or voltage balancing capacitors

Requires the least number of components considering there are no extra clamping diodes are voltages balancing

#### **III. MODULATION TECHNIQUES**

Mainly the power electronic converters are operated in the "switched mode". Which means the switches within the converter are always in either one of the two states turned off (no current flows), or turned on (saturated with only a small voltage drop across the switch). Any operation in the linear region, other than for the unavoidable transition from conducting to nonconducting, incurs an undesirable loss of efficiency and an unbearable rise in switch power dissipation. To control the flow of power in the converter, the switches alternate between these two states (i.e. on and off). This happens rapidly enough that the inductors and capacitors at the input and output nodes of the converter average or filter the switched signal. The switched component is attenuated and the desired DC or low frequency AC component is retained. This process is called Pulse Width Modulation (PWM), since the desired average value is controlled by modulating the width of the pulses.

## A. PWM Techniques

The fundamental methods of pulse-width modulation (PWM) are divided into the traditional voltage-source and current-regulated methods. Voltage-source methods more easily lend themselves to digital signal processor (DSP) or programmable logic device (PLD) implementation. However, current controls typically depend on event scheduling and are therefore analog implementations which can only be reliably operated up to a certain power level. In discrete current-regulated methods the harmonic performance is not as good as that of voltage-source methods. A sample PWM method is described below.

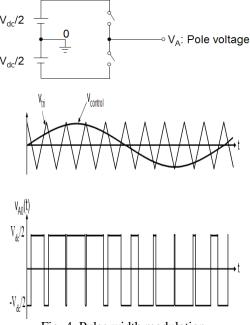

Fig. 4. Pulse width modulation

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 4. Issue 6. June 2016

Different PWM techniques applicable to inverters are:

- 1. Single-pulse modulation

- 2. Multiple-pulse modulation

- 3. Selected harmonic elimination (SHE) PWM

- 4. Sinusoidal-pulse PWM (SPWM)

- 5. Harmonic Injected Modulation

- 6. Space vector-pulse PWM (SVPWM)

## IV. SINE PULSE WIDTH MODULATION(SPWM)

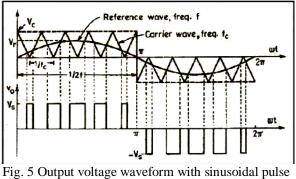

The SPWM technique is based on the comparison of a carrier signal and a pure sinusoidal modulation signal. It was introduced by Schonung and Stemmler in 1964 as reported in (Kumar et al. 2008). The utilization rate of the DC voltage for traditional sinusoidal PWM is only 78:5% of the DC bus voltage, which is far less than that of the six-step wave (100%). Improving the utilization rate of the DC bus voltage has been a research focus in power electronics. The sinusoidal pulse-width modulation (SPWM) technique produces a sinusoidal waveform by filtering an output pulse waveform with varying width. A high switching frequency leads to a better filtered sinusoidal output waveform. The desired output voltage is achieved by varying the frequency and amplitude of a reference or modulating voltage.

modulation

The variations in the amplitude and frequency of the reference voltage change the pulse-width patterns of the output voltage but keep the sinusoidal modulation. When triangular carrier wave has its peak coincident with zero of the reference sinusoid, there are N=fc/2f pulses per half cycle; Fig. has five pulse. In case zero of the triangular wave of coincides with zero of the reference sinusoid, there are (N-1) pulses per half cycle.

# V. SPACE VECTOR PULSE WIDTH MODULATION A. Simulations And Result (SVPWM)

The space vector modulation (SVM) method is an advanced, computation-intensive PWM method and is possibly the best method among the all PWM techniques for variable-frequency drive application. Because of its superior performance characteristics, it has been finding wide spread application in recent years.

SVM is an algorithm for the control of pulse width modulation (PWM). It is used for the creation of alternating current (AC) waveforms; most commonly to drive three phase AC powered motors at varying speeds

from DC using multiple class-D amplifiers. There are various variations of SVM that result in different quality and computational requirements. One active area of development is in the reduction of total harmonic distortion (THD) created by the rapid switching inherent to these algorithms.

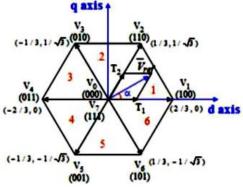

Fig. 6 Basic switching vectors and sectors

To implement space vector modulation a reference signal  $V_{ref}$  is sampled with a frequency fs (Ts = 1/fs). The reference signal may be generated from three separate phase references using the Clarke's transform. The reference vector is then synthesized using a combination of the two adjacent active switching vectors and one or both of the zero vectors. Various strategies of selecting the order of the vectors and which zero vector(s) to use exist. Strategy selection will affect the harmonic content and the switching losses. So Space Vector Modulation can be implemented by the following steps:

- Step 1. Determine  $V_d$ ,  $V_q$ , Vref, and angle ( $\alpha$ ) •

- Step 2. Determine time duration T1, T2, T0 •

- Step 3. Determine the switching time of each transistor of inverter.

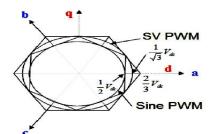

Fig.7 Locus Comparison of Maximum Linear Control Voltage in Sine PWM and SVPWM

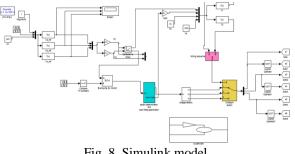

Simulink model of svm for two level inverter

Fig. 8. Simulink model

IJIREEICE

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 4. Issue 6. June 2016

#### VI. CONCLUSION

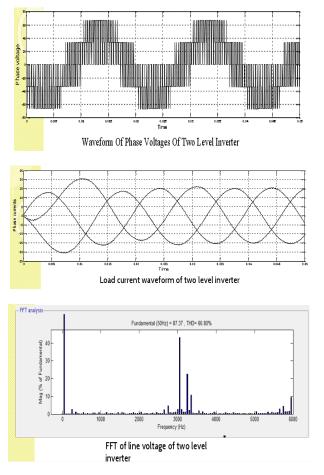

Simulink model for the two techniques- SPWM and SVM (proposed technique) have been developed and tested in the MATLAB/Simulink environment. From the results obtained it is concluded that as the level of inverter increases the fundamental component increases and THD reduces.

On comparing the result of three, five and seven level inverters employing SVM and SPWM, SVM is found superior to SPWM in terms of fundamental and THD.

Simulation results of two-level SVM confirm that the amplitude of line to line voltage is as high as DC bus voltage in SVM technique. Among three switching state and four switching state technique, though THD of four switching inverter increases slightly, but lower order harmonics are reduced and the current harmonics are much less in inverter employing SVM with four switching states.

| TABLE 1 | 1 |

|---------|---|

|---------|---|

| Sr.No. | Harmonic<br>order | Using three<br>switches | Using four<br>Switches |

|--------|-------------------|-------------------------|------------------------|

| 1.     | 5                 | 2.60                    | 1.14                   |

| 2.     | 7                 | 1.20                    | 0.86                   |

#### ACKNOWLEDGMENT

The acknowledge support is provided by G.Z.C.E.T. faculty for the collection of data. I would like to express my special thanks of gratitude to my teacher **Daljit Kaur** (G.Z.S. Campus CET, Bathinda) and my friends and colleagues.

#### REFERENCES

- [1] Maheswari, S. Mahendran, Dr. I. Gnanambal, "Implementation of Fundamental Frequency Switching Scheme on Multi –Level Cascaded HBridge Inverter Fed Three Phase Induction Motor Drive" Wulfenia journal, Klangfurt, Austria, Vol 19, No. 8, pp10-24,2012.

- [2] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral pointclamped PWM inverter," IEEE Trans. Ind. Appl., vol IA-17, no. 5, pp. 518- 523, sep./oct.1981.

- [3] J. Rodriguez, J. S. Lai, and F.Z. Peng, "Multilevel inverters: A survey of topologies, controls, and applications," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724-738, Aug. 2002.

- [4] F.Z.Peng, J. S. Lai, J. W. McKeever, and J. Van Coevering, "A multilevel voltage-source inverter with separate DC sources for static var generation," IEEE Trans. Ind. Appl., vol.32, no.5,pp.1130-1138,sep./oct. 1996.

- [5] [ S. De, D. Banerjee I, K. Siva kumar, K. Gopakumar, R. Ramchand, and C. Patel, "Multilevel inverters for low-power application," IET Power Electron., vol. 4, no. 4, pp. 384-392,2011.

- [6] Javad Ebrahimi, Ebrahim Babaei and Goverg B. Gharehpetian "A New Topology of Cascaded Multilevel Converter with Reduced Number of Components For High Voltage Applications," IEEE Trans. Power Electronics, Vol.26, NO.11, Nov. 2011.

- [7] E. Babaei and S. H. Hosseini, "New casacded multilevel inverter topology with minimum number of switches," Elsevier J. Energy Convers. Manage. vol. 50, no. 11, pp. 2761-2767, Nov. 2009.

- [8] Leon M. Tolbert, John Chiasson, Keith McKenzie, Zhong Du, Elimination of harmonics in a multilevel converter with non equal DC sources, IEEE transaction on Industry applications, Vol.41, 2005

- [9] José Rodríguez, Jih-Sheng Lai, Fang Zheng Peng, Multilevel Inverters: A Survey of Topologies, Controls and Applications, IEEE transaction on Industry Electronics, Vol.49, 2002

## BIOGRAPHY

**Jaspreet Dhillon** has obtained her B.E and is pursuing her PG (Power Engineering) from GZS Campus CET, Bathinda. Areas of her interest is Power electronics and Electrical Machines.